maxplus2是一款功能强大的PLD开发软件,可以帮助用户更好的开发FPGA/CPLD。用户可以使用该软件完成设计输入、组件适配、时序模拟、功能模拟等流程,提高工作效率。软件已成功破解,内置完美破解补丁,可免费解锁所有功能。

【软件功能】

1.设计输入。在传统的设计中,设计者通过应用传统的原理图输入方法来开始设计。从20世纪90年代初开始,Verilog、VHDL、AHDL等硬件描述语言的输入法被广泛应用于大型设计中。

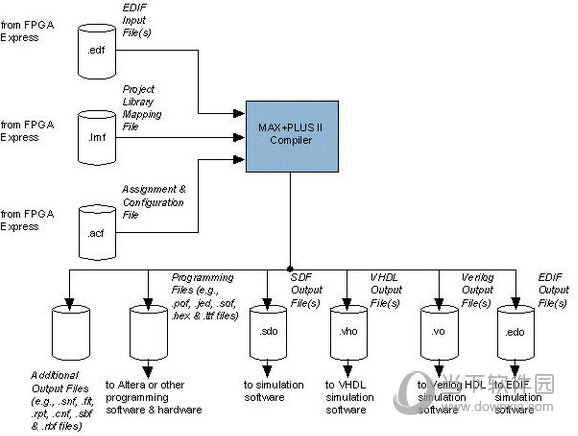

2.预仿真(功能仿真),设计的电路在布局布线前必须验证电路功能是否有效。(在ASCI设计中,这一步称为首次签署)在PLD设计中,这一步有时会被跳过。

3.设计编译,在设计输入后,有一个从高层系统行为设计到门级逻辑电路设计的翻译过程,即把设计输入的一种或几种数据格式(网表)转换成软件可识别的一些数据格式(网表)。

4.优化:对于上述综合生成的网表,根据布尔方程功能等价的原则,用更小更快的综合结果替换一些复杂的单元,用指定的库进行映射,生成新的网表,这是降低电路规模的必由之路。

5.布局和布线。在PLD设计中,利用PLD厂商提供的开发软件(如Maxplus2)可以一次性自动完成步骤3-5。

6.后仿真(时序仿真)需要利用版图中获得的精确参数再次验证电路的时序。(在ASCI设计中,这一步称为第二次签署)。

7.生产、布线和后期仿真完成后,就可以开始ASCI或PLD芯片的生产了。

【软件特色】

1.开放接口,支持与Cadence、Exemplarlogic、Mentor Graphics、Synplicty、Viewlogic等公司提供的EDA工具的接口。

2.独立于结构,系统的核心编译器(Complier)支持FLEX10K、FLEX8000、FLEX6000、MAX9000、MAX7000、MAX5000以及Altera公司的经典可编程逻辑器件,提供全球唯一真正独立于结构的可编程逻辑设计环境。

3.完全集成。设计输入、处理和比较功能都集成在一个统一的开发环境中,可以加快动态调试速度,缩短开发周期。

4.丰富的设计库,提供丰富的库单元供设计师调用,包括所有74系列器件,多种特殊逻辑函数(宏函数)和一个新的参数化的Mage-Function。

5.模块化工具。设计师可以从各种设计输入、处理和比较选项中进行选择,以定制设计环境。

6.硬件描述语言。该软件支持各种HDL设计输入选项,包括VHDL,Verilog HDL和Altera自己的硬件描述语言AHDL。

7.Opencore特性。该软件具有开放核心的特点,允许设计师添加他们认为有价值的宏功能。

【破解说明】

1.运行安装程序。请将“PCALTERA32BIT”目录中的。

单击安装软件max plus ii基线软件安装软件。

2.首次运行MAX plus II时,会弹出“遵守协议”对话框。

用鼠标将内容下拉到最后,选择“确定”。

3.将安装盘目录下的授权文件复制到MAX plus II的安装目录下(如‘C:maxplus 2’目录)。

4.再次启动MAX plus II并选择菜单[选项]-[设置]功能。

在弹出的对话框中,按“浏览”按钮,选择刚刚复制的授权文件。

退出,确认,退出MAX plus II开发环境,再次运行MAX plus II。